초고속 프로세스에서 이미지 기반 제어를 보장하는 최첨단 이미지 처리 구현

Columbia University, Drexel University, Fermilab, Lehigh University의 연구진은 Euresys 프레임 그래버와 CustomLogic기능을 통해 카메라 기반 고속 토카막 플라스마 제어 루프에서 신호 수집과 제어 명령 간의 시간을 크게 단축하여 핵융합 에너지를 위한 새로운 기능을 개발할 수 있었습니다.

“Vision-in-the-Loop”의 또 다른 예에서 플라스마 제어 요구사항은 이처럼 복잡한 제어 논리에 대해 전례 없는 속도에 도달합니다.

애플리케이션

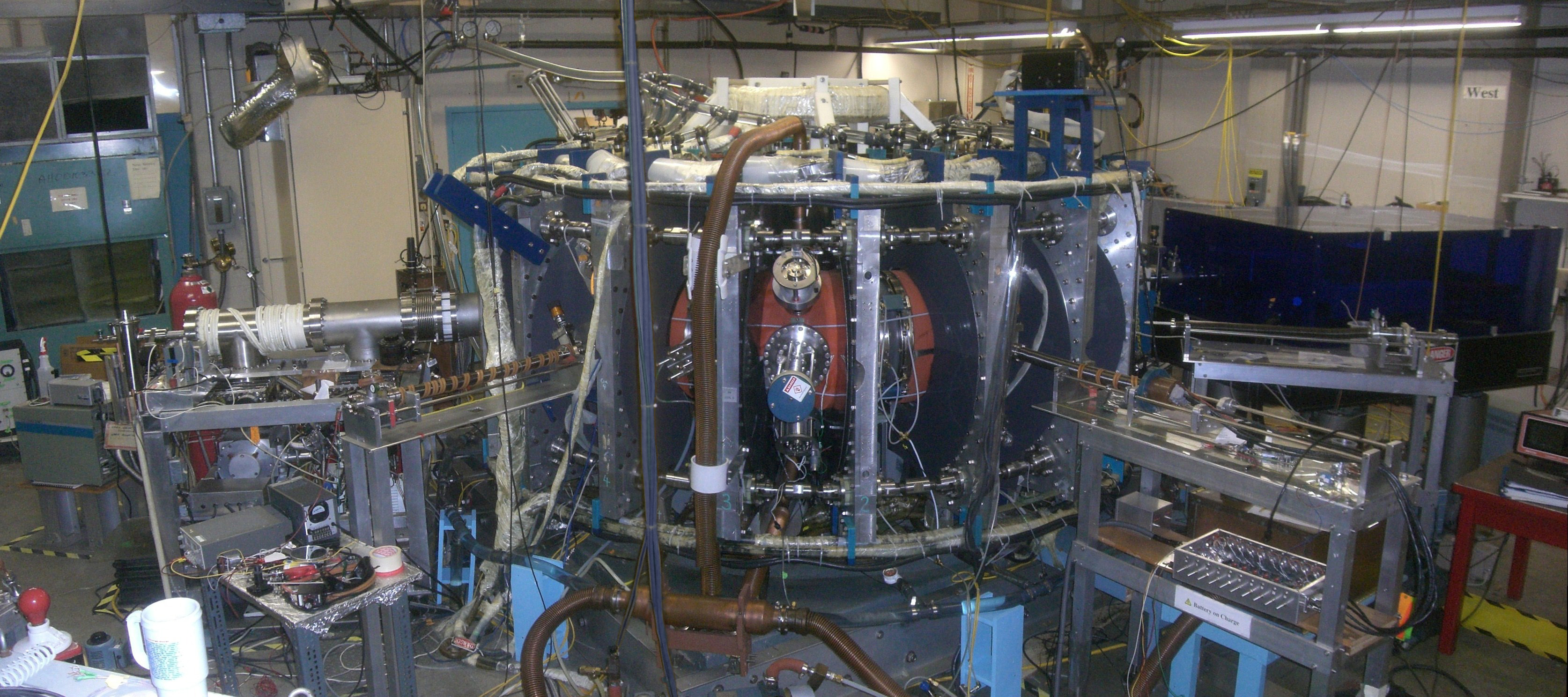

토카막은 자기장을 이용하여 고온의 플라스마를 과학자들이 원환이라고 부르는 도넛 모양으로 가두는 기계입니다. 핵융합 에너지 과학자들은 토카막이 현재 미래 핵융합 발전소를 위한 선도적인 플라스마 봉입 개념 중 하나라고 믿고 있습니다.

자기 봉입 핵융합 장치에서 능동 피드백 제어는 플라스마 불안정성을 완화하고 견고한 고성능 작동을 구현하는 데 바람직합니다. 광학 고속 카메라는 강력하고 비침습적 진단 기능을 제공하며 이러한 애플리케이션에 적합할 수 있습니다.

그림 2 – Columbia HBT-EP 토카막 – © D. Shiraki

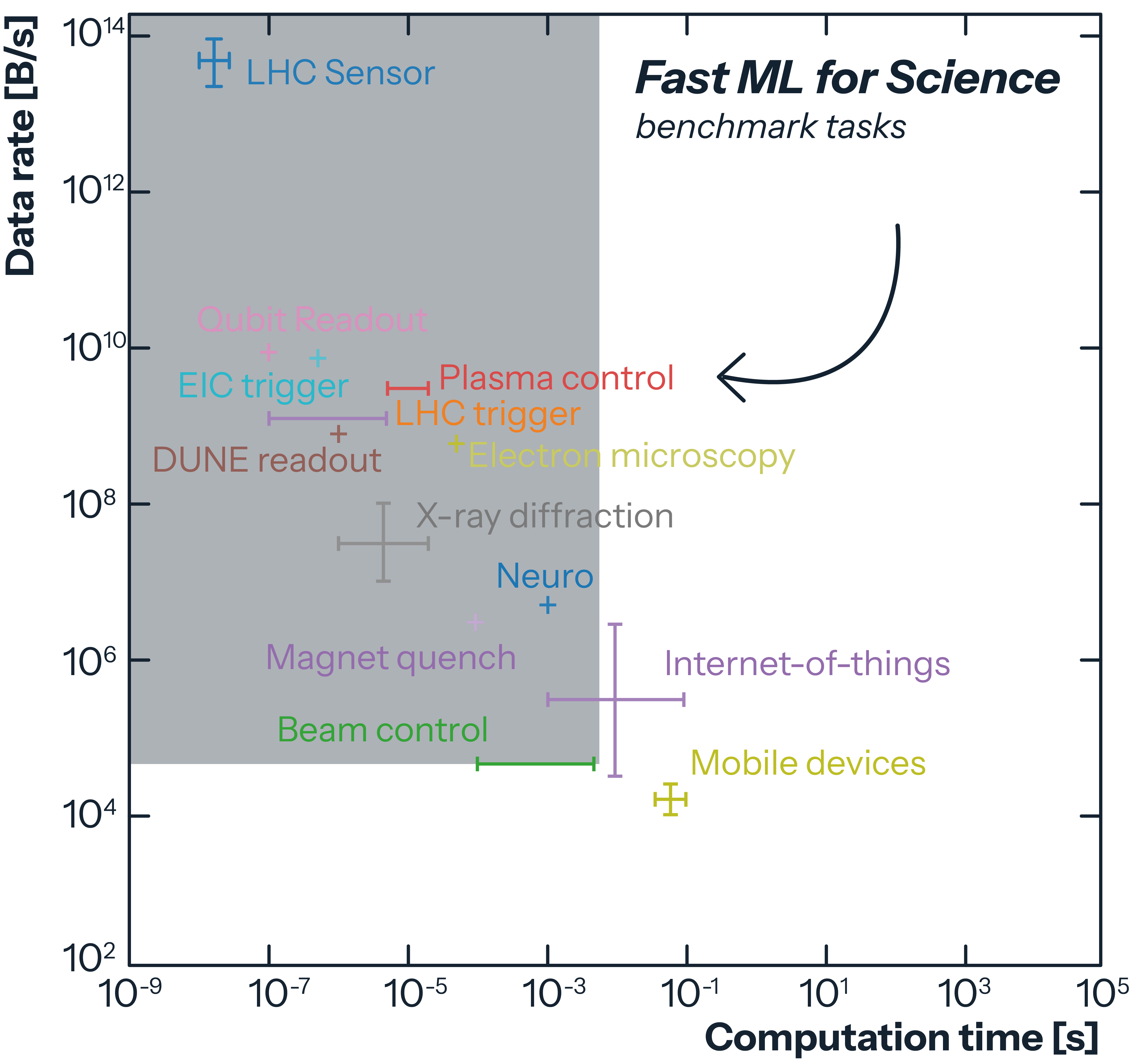

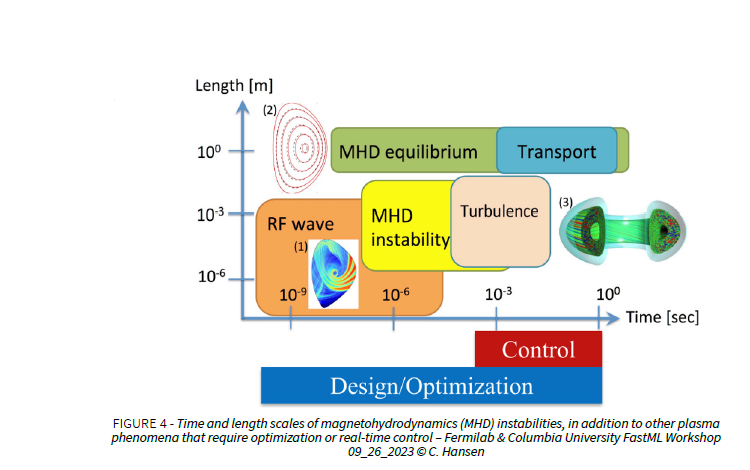

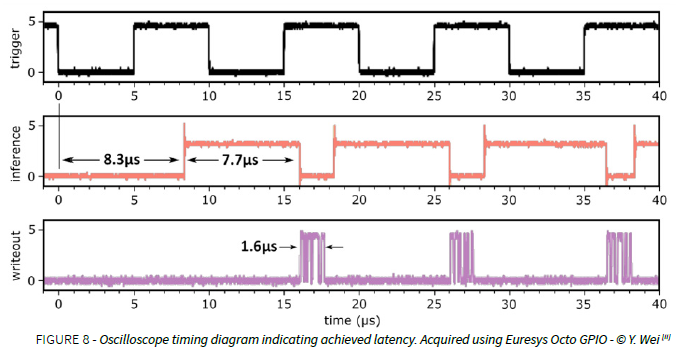

연구팀은 논문에서 Columbia University의 HBT-EP 융합 실험에서 플라스마 제어를 위한 현장 FPGA(Field Programmable Gate Array) 하드웨어에서 100,000fps가 넘는 속도로 빠른 카메라 데이터를 처리한 방법을 설명했습니다. 그 목적은 자기유체역학(MHD) 불안정성 진화를 추적하고 실시간으로 제어 요청을 생성하는 것입니다. 이를 위해 연구팀은 프레임 그래버에 내장된 FPGA에 컨볼루션 신경망(CNN) 모델을 구현하여 17.6µs의 트리거-출력 지연 시간과 최대 120,000fps의 처리량을 달성할 수 있었습니다.

그림 3 – 다양한 프로세스의 데이터 전송 속도 대 계산 시간 – 과학을 위한 빠른 ML(Fast ML for Science) – © N. Tran

선택된 솔루션

하드웨어 플랫폼은 다음과 같이 구성되었습니다.

- AMETEK Phantom S710™ 카메라(최대 7Gpx/초(87.5Gbps)의 스트리밍 성능, 예: 1,280 x 800에서 7,275fps,

- 카메라 출력을 수용하는 Euresys Coaxlink Octo프레임 그래버.

이 경우 데이터를 CPU 또는 GPU로 전송하여 중앙 처리하면 10µs 범위인 애플리케이션의 응답성 요구 사항을 충족하지 못했을 것입니다.

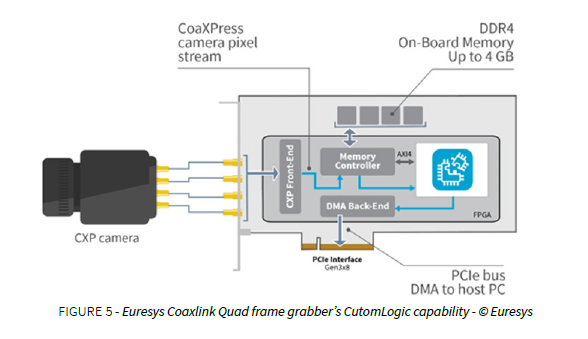

Euresys의 CustomLogic을 사용할 수 있게 되면서 연구자들은 Coaxlink Octo 프레임 그래버에서 직접 자체 플라스마 제어 알고리즘(CNN 추론)을 프로그래밍하여 플라즈마 역학에 상응하는 지연 시간을 달성할 수 있는 특별한 기회를 얻게 되었습니다.

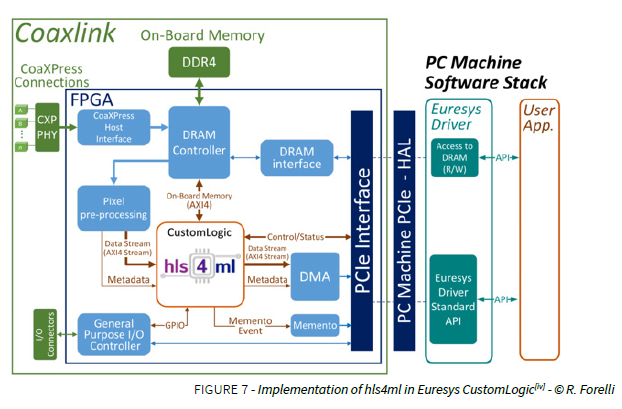

Coaxlink CustomLogic은 AMD Vivado™ 개발 도구를 사용하여 프로그래밍할 수 있습니다. FPGA 리소스는 다음의 세 가지 주요 용도로 할당됩니다:

- CoaXPress 프로토콜,

- 내부 카드 관리,

- 사용자 정의 CustomLogic, 이 경우 제어 알고리즘의 신경망 모델 및 제어 출력 요청 계산.

팀은 프레임 그래버 FPGA 칩의 리소스 제약을 충족하면서 평소보다 더 강력한 제어 알고리즘을 구현해야 하는 과제를 맡았습니다. 이를 위해 연구팀은 프레임 그래버의 FPGA에 모델을 합성하고 배포하기 전에 오픈 소스인 hs4ml(머신 러닝을 위한 고수준 합성)[iii] 패키지를 사용하여 모델을 변환하고 최적화했습니다.

Coaxlink Octo I/O는 플라스마 제어 시스템(개발 중인 외부 하드웨어)과 직접 인터페이스되며, 이미지 데이터는 PCIe 버스를 통해 호스트 컴퓨터로 전송되어 제어 루프 외부에서 후처리 됩니다.

이 구현은 궁극적으로 지연 시간을 CNN 모델 자체에 대해 7.7µs, 수집 트리거에서 출력 제어 요청까지 총 17.6µs로 단축했으며, 최대 120kfps의 파이프라인 프레임 속도로 실행할 수 있어 토카막에서 MHD 불안정성의 실시간 제어에 대한 요구 사항을 충족합니다.

도구 키트

개발자는 AMD Vivado™ 도구 외에도 다음과 같은 추가적인 Euresys 도구를 통해 폭넓은 지원을 받을 수 있습니다.

- 10MHz RS422 차동 IO를 통해 펌웨어 모델 지연 및 처리량을 쉽게 벤치마킹할 수 있는 범용 I/O 인터페이스(위 그림 참조).

- 타임스탬프가 찍힌 이벤트의 정확한 타임라인과 함께 콘텍스트 정보 및 로직 분석기 보기를 제공하는 Memento 이벤트 로깅 도구. 애플리케이션 개발 및 디버깅 시 유용한 지원.

- 사용자가 Coaxlink Driver API를 통해 사용자 로직 내에서 레지스터를 읽고 쓸 수 있게 하는 제어/상태 인터페이스.

- Coaxlink CustomLogic SDK와 함께 제공되며 템플릿으로 사용하기 위한 참조 설계. 참조 설계는 사용자가 사용할 수 있는 모든 인터페이스를 노출합니다.

결론

이러한 CustomLogic의 구체적인 구현은 연구자들이 자체 맞춤형 알고리즘을 구현할 수 있도록 Euresys 솔루션이 최첨단 이미지 처리에 대한 액세스를 어떻게 제공하는지 보여줍니다.

Coaxlink 프레임 그래버는 타사가 (CPU/GPU 기반의 상위 레벨 프로그래밍 대신) FPGA 레벨에서 빠르게 실행되는 로우 레벨 커스텀 로직을 구현할 수 있도록 함으로써, 사용자가 까다로운 프로세스 제어 타이밍 제약 조건을 처리할 수 있게 해 줍니다.

이는 여기서 구체적으로 설명한 것 외에도 시간 제약이 있는 다른 많은 애플리케이션 영역에서도 해당될 수 있습니다.

연쇄 프로세스에서 병목 현상이 제거될 때마다 더 새롭고 더 까다로운 애플리케이션 및 사양의 영역으로 나아갈 수 있는 길이 열립니다. 또한 Euresys는 이미 구리 또는 광섬유 연결을 통해 더 높은 용량을 수용함으로써 더욱 정밀한 제어를 할 수 있는 길을 닦아가고 있습니다. 또한 Euresys에서 제공하는 것과 같은 이미지 전송/처리 링크는 구리 또는 광섬유 연결을 통해 훨씬 더 높은 용량을 제공함으로써 이러한 요구 사항을 충족할 것입니다.

프로젝트에 대한 자세한 내용은 ArXivportalhttps://arxiv.org/abs/2312.00128과 GitHub에서 구현에 대한 소개 튜토리얼에서 확인할 수 있습니다.

Euresys 프레임 그래버와 CustomLogic에 대한 자세한 내용은 여기에서 확인할 수 있습니다. https://www.euresys.com/ko/products/serie/coaxpress/

[i] US Department Of Energy (DOE) Office of Science

[ii] Low latency optical-based mode tracking with machine learning deployed on FPGAs on a tokamak [Y. Wei, R.F.Forelli, C. Hansen, J. P. Levesque, N. Tran, J. C. Agar, G. Di Guglielmo, M. E.Mauel, and G. A. Navratil]

[iii] Welcome to hls4ml’s documentation! — hls4ml 0.8.1 documentation (fastmachinelearning.org)

[iv] Euresys, D209ET-Coaxlink CustomLogic User Guide-eGrabber 16.0.2.2128, Euresys S.A., Seraing, Belgium (2021)