最先端の画像処理を実装し、超高速プロセスにおける画像ベースの制御を実現

コロンビア大学、ドレクセル大学、Fermilab、およびリーハイ大学の研究チームは、EuresysフレームグラバーとCustomLogicの機能を利用することで、カメラを使用した高速トカマクプラズマ制御ループにおける信号の取得と制御コマンドの間の時間を大幅に短縮し、核融合エネルギーの新たな可能性を開発することができました。

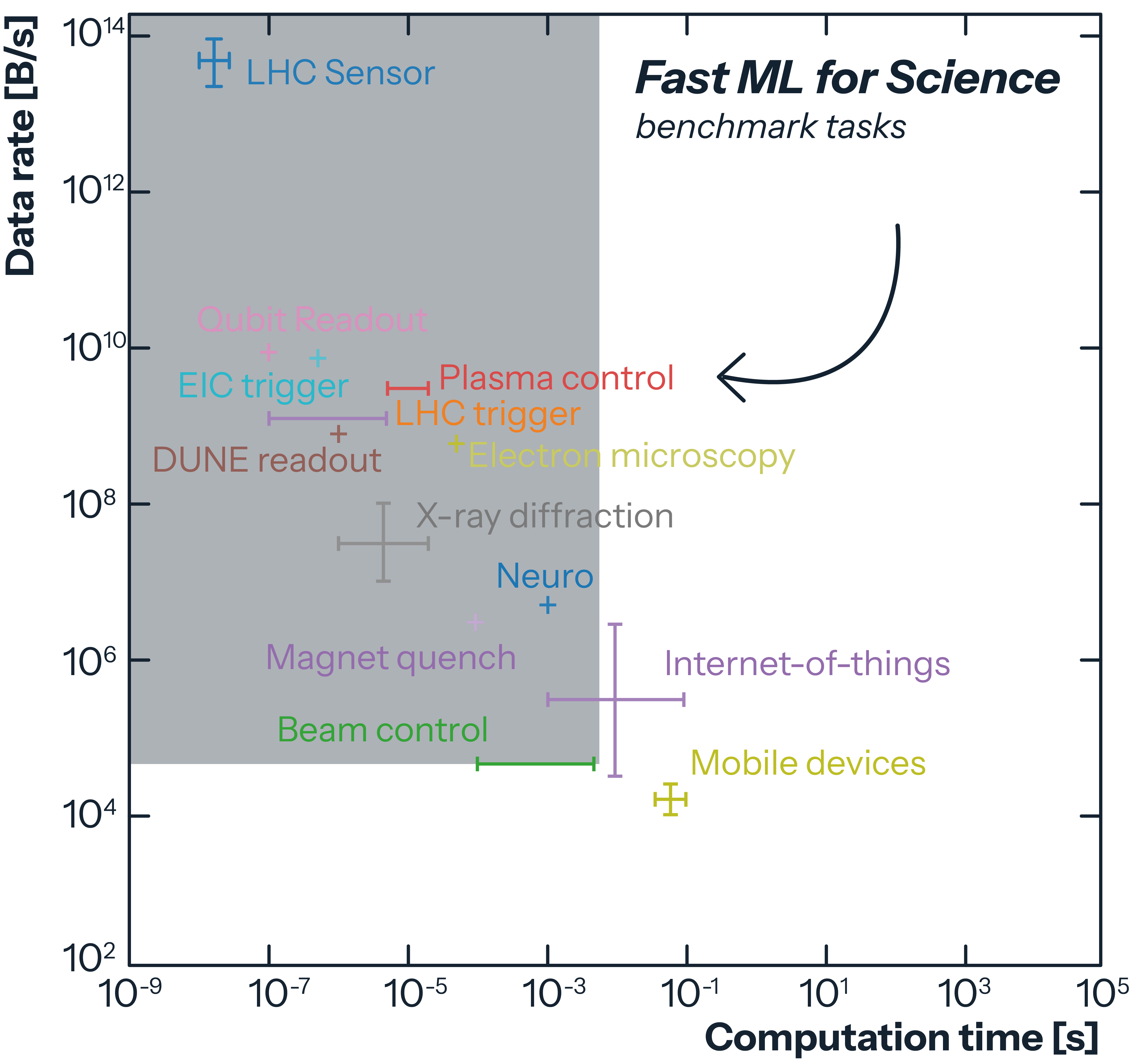

「Vision-in-the-Loop」方式の別の例においては、プラズマ制御の要件は、このような複雑な制御ロジックに対して前例のない速度に達しています。

用途

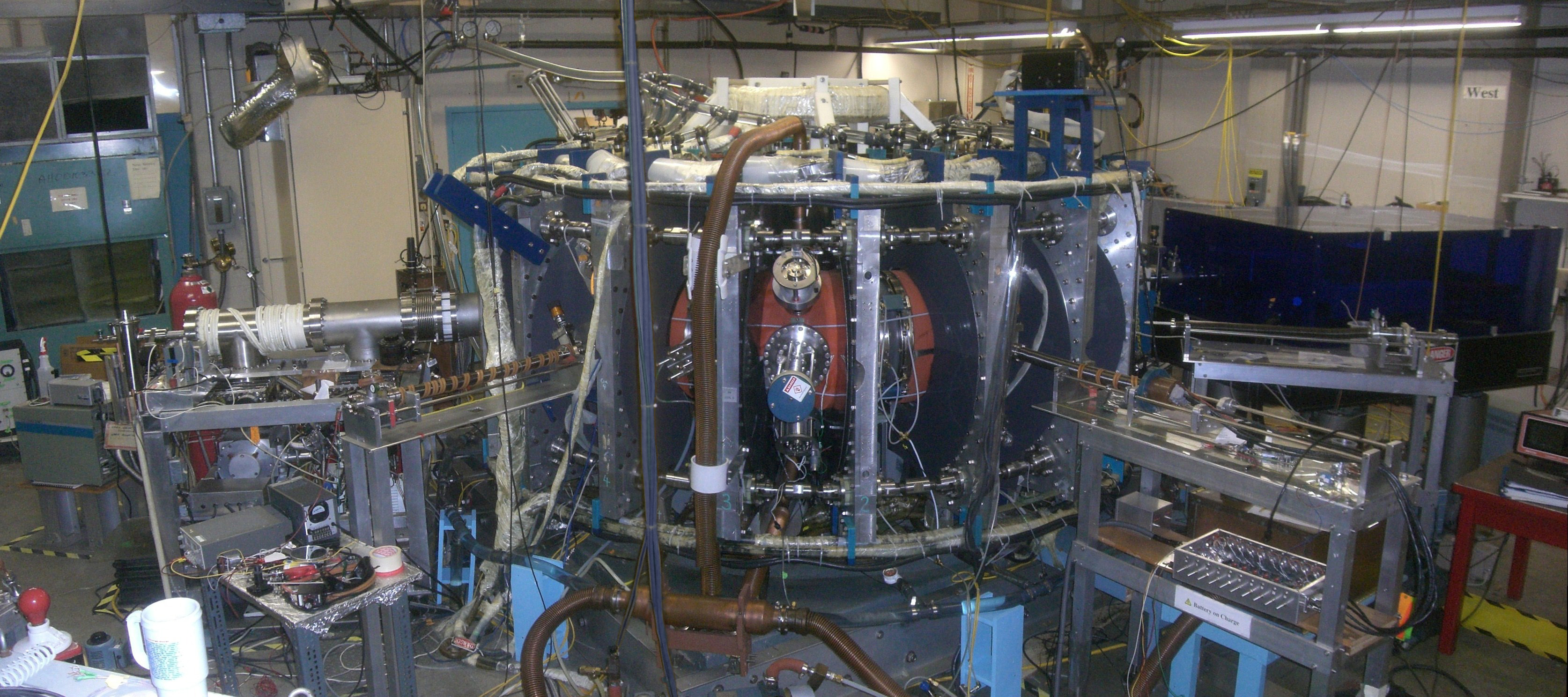

トカマクは、科学用語でトーラスと呼ばれるドーナツ状の磁場を使用して高温プラズマを閉じ込める装置です。核融合エネルギーの科学者は、トカマクが現在、将来の核融合発電所のための主要なプラズマ閉じ込め概念の1つであると考えており、

プラズマの不安定性を軽減し、堅牢で高性能な動作を可能にするためには、磁気閉じ込め核融合装置における能動フィードバック制御が望ましいとしています。光学高速カメラは、強力で非侵襲的な診断を提供するため、これらの用途に適しています。

図2 – Columbia HBT-EP Tokamak – © D. Shiraki

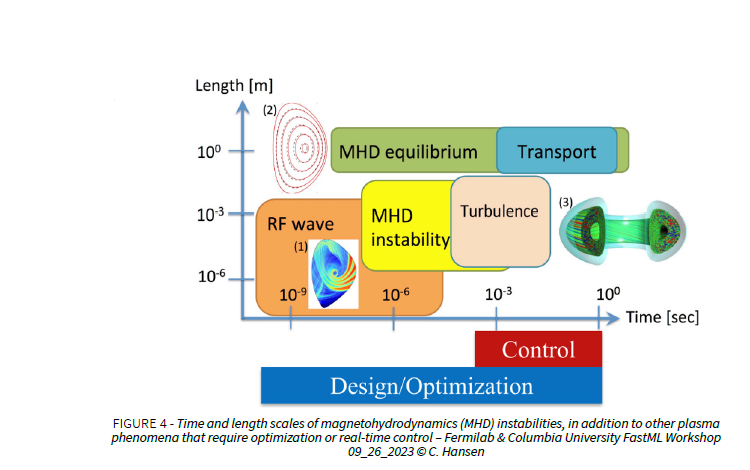

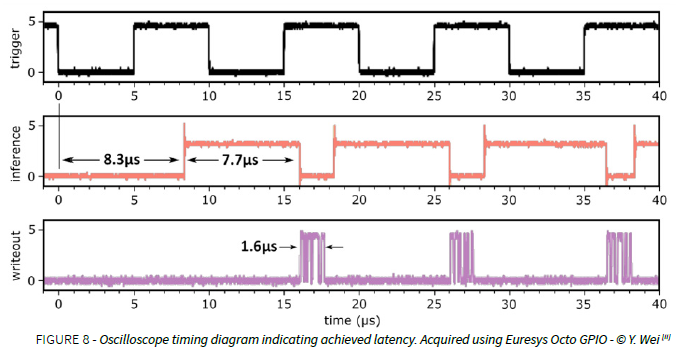

研究チームは論文の中で、コロンビア大学のHBT-EP核融合実験におけるプラズマ制御のために、現場のフィールドプログラマブルゲートアレイ(FPGA)ハードウェアで100,000 fpsを超える速度でカメラデータを処理した方法について述べています。目的は、磁気流体力学(MHD)の不安定性の進化を追跡し、制御リクエストをリアルタイムで生成することです。これを達成するために、チームはフレームグラバーに組み込まれたFPGAにたたみ込みニューラルネットワーク(CNN)モデルを実装し、トリガーから出力まで17.6 µsのレイテンシーと最大120,000 fpsのスループットの達成を実現しています。

図3 – Data rate versus Computation time of various processes – Fast ML for Science – © N. Tran

選択されたソリューション

ハードウェアプラットフォームの構成:

- AMETEK Phantom S710™ カメラ(ストリーミング能力最大7 Gpx/秒(87.5 Gbps)。例: 1,280 x 800で7,275 fps)

- カメラの出力に対応するEuresys Coaxlink Octoフレームグラバー

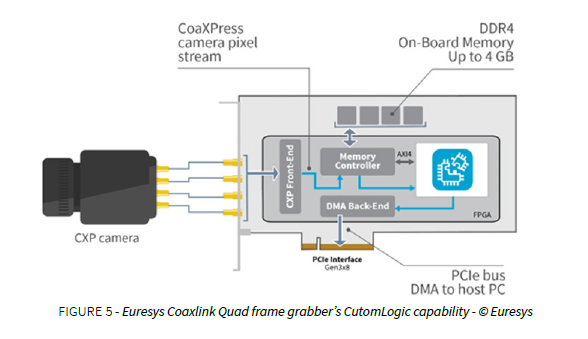

この場合、中央処理のためにデータをCPUまたはGPUに伝送しても、10 µs範囲の用途の応答性要件を満たすことはできません。

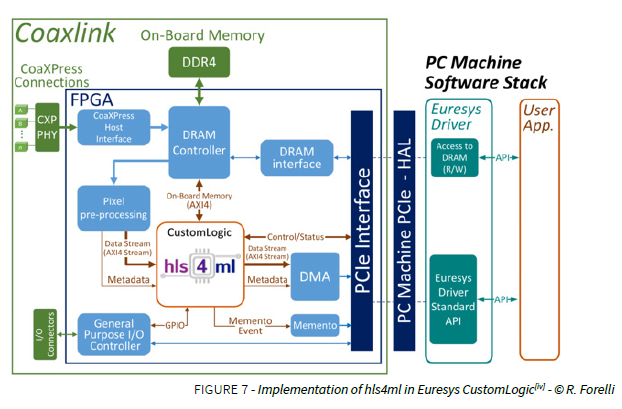

EuresysのCustomLogicを使用することで、研究者は独自のプラズマ制御アルゴリズム(CNN推論)をCoaxlink Octoフレームグラバーで直接プログラミングし、プラズマダイナミクスに適合したレイテンシーを実現できるというまたとない機会を得ることができました。

Coaxlink CustomLogicのプログラミングはAMD Vivado™ 開発ツールを使って行うことができます。FPGAリソースは以下の3つの主な用途に割り当てられます。

- CoaXPressプロトコル

- 内部カード管理

- ユーザー定義のCustomLogic(制御アルゴリズムのニューラルネットワークモデルと制御出力要求の計算を行います)

研究チームは、フレームグラバーFPGAチップのリソースの制約を満たすと同時に、通常よりもパワフルな制御アルゴリズムを実装するという課題に取り組みました。この目的において、オープンソースのHigh-Level Synthesis for Machine Learning (hs4ml)[iii]パッケージを使ってモデルの変換と最適化を行い、合成してからフレームグラバーのFPGAに展開しました。

Coaxlink Octo I/Oはプラズマ制御システム(開発中の外部ハードウェア)に直接接続し、画像データは、制御ループ外部で後処理を行うために、PCIeバスを通じてホストコンピューターに転送されます。

この実装は最終的に、CNNモデル自体のレイテンシーが7.7 µs、取得トリガーから出力制御要求までのレイテンシーが合計17.6 µsを達成し、トカマクにおけるMHD不安定性のリアルタイム制御要件を満たす最大120 kfpsのパイプラインフレームレートで実行することができています。

ツールキット

開発者はAMD Vivado™ ツールに加え、以下のようなEuresysツールから広範な支援を得ています。

- 汎用I/Oインターフェイス(上図)。10MHz RS422差動IOを介してファームウェアモデルのレイテンシーとスループットのベンチマークを簡単に実行できるようにします。

- Mementoイベントログ取得ツール。タイムスタンプが記録されたイベントの正確なタイムラインを、コンテキスト情報とロジックアナライザビューとともに取得できます。用途の開発とデバッグにおいて重要な支援です。

- コントロール/ステータスインターフェイス。ユーザーはCoaxlink Driver API介して、ユーザーロジック内のレジスタの読み取りと書き込みを行えます。

- Coaxlink CustomLogic SDKに付属のリファレンスデザイン。テンプレートとして使用します。リファレンスデザインでは、ユーザーが使用できるすべてのインターフェイスが公開されています。

まとめ

CustomLogicのこの特定の実装では、研究者が独自のカスタムアルゴリズムを実装する上で、Euresysソリューションがどのようにして最先端の画像処理へのアクセスを提供しているかが示されています。

Coaxlinkフレームグラバーを使用すると、サードパーティが(CPU/GPUベースの高位プログラミングではなく)低レベルの高速実行カスタムロジックをFPGAレベルで実装できるため、ユーザーは厳しいプロセス制御タイミング制約に対処することができます。

これは、ここで具体的に論じられている用途に限らず、時間の制約がある他の多くの用途にも適用可能です。

チェーンプロセスにおけるボトルネックが解消されるたびに、より新しく、さらに要求が厳しくなることの多い用途や仕様に対処する道が開かれます。Euresysはすでに、銅線または光ファイバ接続による高容量化に対応することで、さらに精密な制御を実現にする道を切り開いています。Euresysが提供するような画像伝送/処理リンクは、銅線または光ファイバ接続によるさらなる高容量化を提供することで、これらの要件を満たすようになるでしょう。

このプロジェクトに関する詳細は、ArXivportal(https://arxiv.org/abs/2312.00128)および実装に関するGitHubの導入チュートリアルをご覧ください。

EuresysフレームグラバーおよびCustomLogicに関する詳細はこちらをご覧ください: https://www.euresys.com/ja/products/serie/coaxpress/

[i] US Department Of Energy (DOE) Office of Science

[ii] Low latency optical-based mode tracking with machine learning deployed on FPGAs on a tokamak [Y. Wei, R.F.Forelli, C. Hansen, J. P. Levesque, N. Tran, J. C. Agar, G. Di Guglielmo, M. E.Mauel, and G. A. Navratil]

[iii] Welcome to hls4ml’s documentation! — hls4ml 0.8.1 documentation (fastmachinelearning.org)

[iv] Euresys, D209ET-Coaxlink CustomLogic User Guide-eGrabber 16.0.2.2128, Euresys S.A., Seraing, Belgium (2021)