データ (ピクセル) ストリームインターフェイス

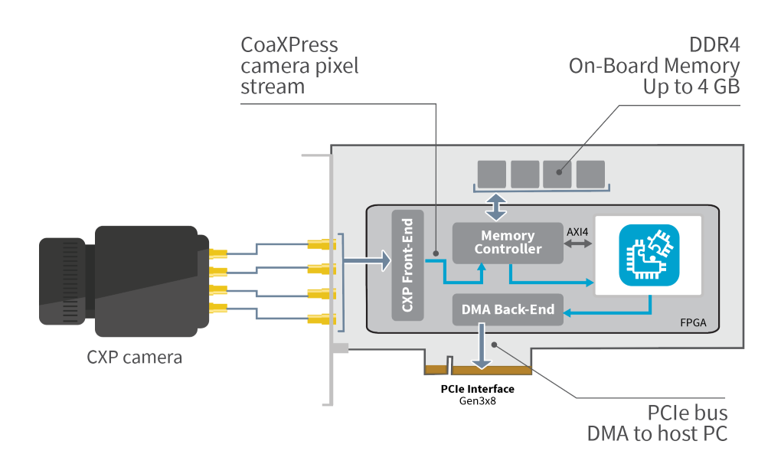

イベント データストリームインターフェイスは、AMBA AXI4-Streamプロトコルに基づいています。ソース側では、このインターフェイスは、ユーザーロジックにCoaXPressデバイス (CoaXPressカメラなど) から取り込んだ画像を提供します。ターゲット側では、データストリームインターフェイスは、ユーザーロジックによって生成された結果画像/データをPCI Express DMAバックエンドチャネルに転送します。

DDR4メモリインターフェイス

DDR4メモリインターフェイスは、AMBA AXI4プロトコルに基づいています。

MEMENTOイベントインターフェイス

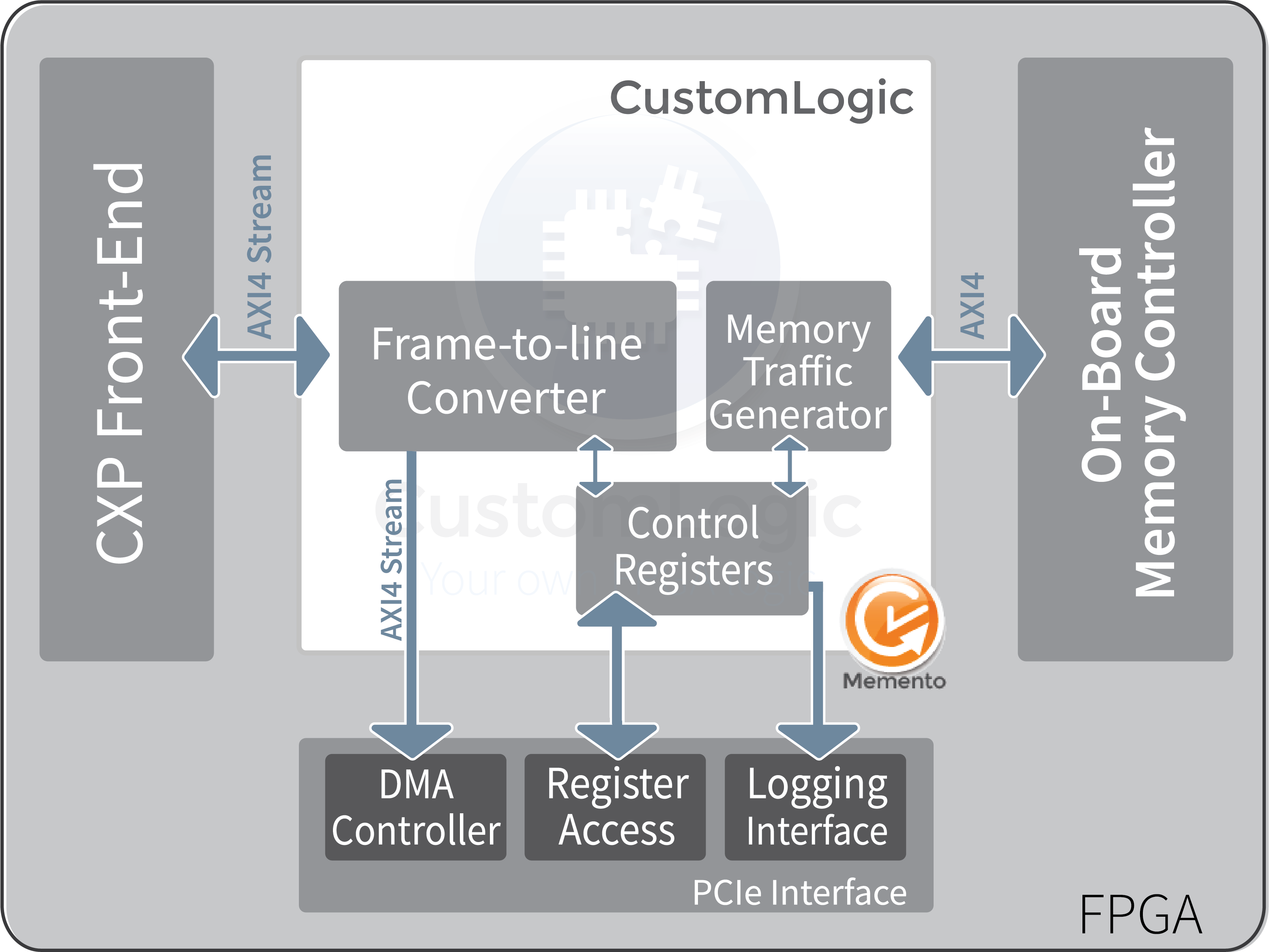

Mementoイベントインターフェイスを使用すると、ユーザーロジックは、1μs. の精度で、タイムスタンプ付きのイベントをMementoロギングツールに送信することができます。タイムスタンプ付きのイベントともに、2つの32ビット引数がMementoに送信されます。

コントロール/ステータスインターフェイス

コントロール/ステータスインターフェイスによって、ユーザーは、Coaxlink Driver APIを介して、ユーザーロジック内のレジスタの読み取りと書き込みを行うことができます。

リファレンスデザイン

Coaxlink CustomLogic SDKには、テンプレートの代わりに使用できるリファレンスデザインが含まれています。リファレンスデザインは、ユーザーが使用できるすべてのインターフェイスを紹介しています。次の機能ブロックダイアグラムが備わったXilinx Vivadoプロジェクトです。

デバッグ機能

CustomLogicの使用には、追加のハードウェアは不要です。別売りの3613 JTAG Adapter Xilinx for Coaxlinkを使用すると、XilinxプログラマをCoaxlink FPGAに接続してデバッグ機能を使用することができます。

EURESYS CUSTOMLOGICについて

CUSTOM LOGICと互換性のあるEURESYS製品